Van PCIe-kaarten die je zelf kan kopen tot kant-en-klare instances in de publieke cloud: De FPGA is aan een sterke opmars bezig. Waar komt die populariteit vandaan en welk voordeel bieden ze tegenover een cpu of gpu?

Field Programmable Gate Arrays, of FPGA in mensentaal, bestaan al meer dan 35 jaar en ondervinden de laatste jaren een flinke boost in populariteit. De chips kruipen uit de niches waarin ze jarenlang trouw dienst deden en werken zich in steeds meer mainstream hardware zoals servers. De voornaamste cloudplatformen bieden vandaag instances met FPGA’s aan. We kruipen achter de webcam voor een gesprek met Adam Scraba, Director of Product Marketing Data Center en AI bij Xilinx. Zijn bedrijf stond in 1985 aan de wieg van de FPGA en zag het nut van de chips doorheen de jaren evolueren.

FPGA?

FPGA’s verschillen van klassieke microchips omwille van hun flexibiliteit en programmeerbaarheid. Een traditionele chip zoals een cpu of een gpu is het product van een nauwkeurig uitgedachte architectuur, met precies uitgetekende logische schakelingen en interconnects, geoptimaliseerd op bijvoorbeeld x86-instructies uit te voeren. Een FPGA is bij contrast eerder een blokkendoos met chip-elementen, die de gebruiker met de hulp van software in elkaar kan passen.

lees ook

FPGA: boetseerbare wonderchip voor AI, IoT en machine learning

Een FPGA bestaat uit een enorme hoeveelheid logische blokken zoals AND, OR en NOT-schakelingen, gecombineerd met een veelvoud aan geheugen en interconnects. Hoe de schakelingen aan elkaar hangen, kan je bij een FPGA herdefiniëren, terwijl je bij een traditionele chip vasthangt aan het design van bijvoorbeeld Intel, AMD of Nvidia.

Originele Edge-chip

“De FPGA is de originele edge computingchip”, vertelt Scraba. “De chip lost een interessant probleem op waarbij een toepassing domeinspecifieke acceleratie vraagt. Historisch gezien gaat het dan vooral om embedded devices met unieke compute-vereisten.” Denk daarbij aan IoT-toepassingen zoals switches en routers, maar ook chips voor lucht- en ruimtevaart of toepassingen binnen defensie.

De programmeerbaarheid van de FPGA wint het hier van een all purpose-chip zoals een x86-processor. Hardware-acceleratie betekent in essentie weinig meer dan chips inzetten waarbij de hardware-architectuur beter aansluit bij waar de software om vraagt. Een chip in bijvoorbeeld een satelliet moet op een robuuste manier aan een laag stroomverbruik heel specifieke algoritmes uitvoeren. Onderzoekers kunnen een FPGA op hardwareniveau configureren om daar zo efficiënt mogelijk aan tegemoet te komen.

Nieuw domein

Met de opkomst van machine learning, AI en aanverwante workloads, kwam het idee van hardware-acceleratie ook naar het datacenter. In eerste instantie leek de gpu erg geschikt, omdat die in contrast met een cpu in staat is om erg veel parallelle rekenopdrachten uit te voeren en AI- en machine learning-software vaak naar parallel rekenwerk vraagt. In de praktijk lost de gpu echter maar een deel van de acceleratievraag op. Vanaf hier komen FPGA’s in het spel.

Pas een jaar geleden heeft Xilinx een business unit opgericht die helemaal gefocust is op datacenters.

De realisatie dat de FPGA veel meer kan accelereren dan vandaag gebeurt met de gpu, is relatief nieuw. “Een jaar geleden heeft Xilinx een business unit opgericht die helemaal gefocust is op datacenters”, illustreert Scraba. “Domeinspecifieke acceleratie lost een heleboel problemen op inzake latency en geheugen en daar zitten zowel datacenterproviders als klanten op te wachten.”

FPGA en compute

Xilinx onderscheid momenteel drie belangrijke domeinen waarin FPGA’s aan belang winnen: Compute, opslag en networking. “Binnen compute is er naast klassieke acceleratie met de gpu nog heel wat mogelijk”, weet Scraba. “Heel wat HPC- en inferentie-workloads zijn irregulier parallel.” Dat betekent dat de workload erg variabel is en niet goed schaalt op gpu’s of cpu’s. Gpu’s zijn ideaal voor grote parallelle workloads (heel veel kleine rekensommen), cpu’s zijn goed in het omgekeerde (enkele hele grote en complexe rekensommen). Daartussen bestaat een hele wereld die niet bediend wordt door accelerator-hardware.

“Bij AI-inferentie denken mensen vaak aan convoluted neural networks zoals gebruikt bij beeldherkenning. Die kunnen bijvoorbeeld katten of honden herkennen of kijken wanneer iemand een hoed of een bril draagt. Een dergelijke workload draait goed op een gpu. In de praktijk is het merendeel van de inferentie echter taken als spraakherkenning of recommendation engines achter websites die klanten op maat juiste producten willen aanbieden. Die kunnen veel efficiënter versneld worden met een FPGA.”

Intelligentie in opslag en netwerk

Binnen opslag worden FPGA’s al langere tijd ingezet. Scraba: “Bedrijven zoals Netapp en WD gebruiken de chips voor compressie, deduplicatie en encryptie op hun toestellen. Intussen zien we een evolutie naar de integratie van data analytics-capaciteiten op het opslagmedium zelf. Door FPGA’s op een drive te integreren, wordt de afstand tussen compute en opslag eindelijk zo klein als mogelijk. Het gevolg is een fantastisch lage latency.” Daar komt nog bij dat andere chips in een serveromgeving ontlast worden. Wanneer de SSD op een mediaserver bijvoorbeeld ingebouwde x265-codering bevat, hoeft de processor een mediabestand niet meer zelf te decoderen.

Door FPGA’s op een drive te integreren, wordt de afstand tussen compute en opslag zo klein mogelijk.

In het netwerksegment bestaat eenzelfde beweging. Compute wordt rechtstreeks op de netwerkinterface geïntegreerd en dat gebeurt met FPGA’s. “De vraag naar realtime-diensten is nog nooit zo hoog geweest, maar het is moeilijk om dergelijke diensten op traditionele infrastructuur te bouwen.” Slimme netwerkapparaten ontzorgen opnieuw de aanwezige compute-chips, zijn zuiniger, en houden de latency zo laag mogelijk.

De kracht van de FPGA

De FPGA kan zich zo op heel wat manieren bewijzen, maar wat maakt de chip nu zo geschikt voor bovenstaande workloads? Scraba legt uit: “Kijk eerst eens naar een gpu. Daar zie je honderden rekenkernen, met daarrond geheugen. De belangrijkste uitdaging bij de gpu is om het monster te voeden: hoe zorg je ervoor dat de chip iedere klokcyclus een grote hoeveelheid rekenwerk kan uitvoeren? De oplossing is batching via een pipeline. In een erg parallelle situatie werkt het klaarzetten van batches met rekenwerk erg goed.”

De FPGA is door zijn design in staat om ook in andere situaties snel te werken. “De dingen zijn gebouwd voor zero batching. Op de chip zelf zitten logische schakelingen en geheugen door elkaar. Via software kan je schakelingen en het geheugen aan elkaar linken op een manier die het algoritme dat je wil draaien vrijwel perfect weerspiegelt. Het geheugen en de compute zitten zo altijd op de juiste plaats.”

Bovendien kan de FPGA zonder moeite verschillende types rekenwerk door elkaar uitvoeren. “Vraagt een algoritme om een vermenigvuldiging, wat verder gevolgd door een optelsom, dan moet de chip eerst de vermenigvuldiging uitvoeren, de data wegschrijven naar het geheugen, een context switch uitvoeren, de data opnieuw ophalen en de optelsom maken. Een FPGA kan je programeren om die zaken netjes na elkaar te doen, met telkens de juiste hoeveelheid geheugen op exact de juiste plaats.”

Hardwareversie van je software

Eenvoudig gesteld kan je een FPGA programmeren tot een hardwareversie van je algoritme. Als je dat algoritme uittekent, weet je perfect waar er zware berekeningen nodig zijn, en waar er geheugen nodig is om data opzij te zetten of net te consumeren. Met een goede programmatie zit dat geheugen exact waar het nodig is, in de plaats van aan de rand van de chip.

Eenvoudig gesteld kan je een FPGA programmeren tot een hardwareversie van je algoritme.

Die realiteit zorgt ervoor dat je niet met batches moet werken. Iedere cyclus is honderd procent nuttig en er gaat geen tijd verloren met het schrijven en ophalen naar gedeeld geheugen aan de rand van de chip. Efficiëntie, snelheid en een lagere latency zijn het gevolg. Een gpu is toevallig een chip op maat van bepaalde populaire AI-workloads, een FPGA is programmeerbaar tot chip op maat van andere workloads waarvoor momenteel nog geen specifieke hardware bestaat.

Waarom geen eigen chips?

De programmeerbaarheid van de FPGA speelt tot slot een belangrijke rol in de populariteit ervan. In theorie kan je iedere FPGA-configuratie vervangen door een op maat ontwikkelde chip, en die zal wellicht nog iets efficiënter werken. Chips ontwikkelen en bakken is echter een dure affaire en bovendien zit er geen businessmodel in voor publieke cloudproviders. Zijn kunnen moeilijk honderden verschillende servers met anders geoptimaliseerde accelerators aanbieden. Wat ze wel kunnen doen, is servers met FPGA’s ter beschikking stellen zodat klanten die FPGA zelf kunnen programmeren tot de ideale accelerator voor hun toepassing.

lees ook

Xilinx toont ’s werelds grootste FPGA met 35 miljard transistors

Xilinx komt daaraan tegemoet met zijn Alvio-kaarten. Die bestaan in verschillende maten met ieders een lichte specialisatie. Sommigen zijn bijvoorbeeld meer geschikt om te programmeren in een compute-context, anderen zijn meer op maat van networking of opslag. Die kaarten zijn los te koop, of zitten in cloudservers waar je er als ontwikkelaar mee kan experimenteren.

Programmatiehulp

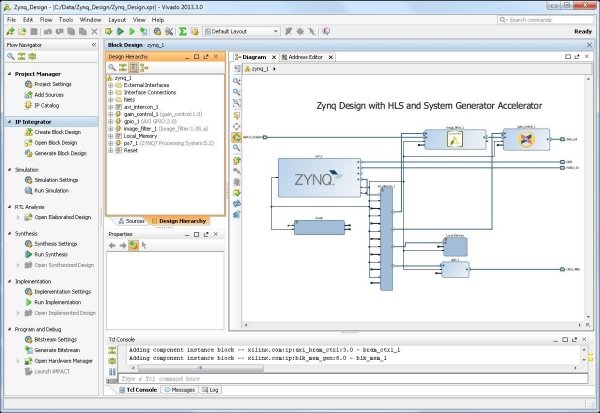

Het is daarbij belangrijk dat de drempel voor de programmering van de FPGA’s steeds lager wordt. “Xilinx verkoopt hardware, maar we hebben heel veel softwareontwikkelaars aan boord”, verduidelijkt Scraba. “We bouwen tools om de programmatie van FPGA’s zo eenvoudig mogelijk te maken.” Hij verwijst naar High Level Synthesis (HLS). Vivado HLS (of ook nog Vitis) is bijvoorbeeld in staat om code in C, C++ of SystemC te vertalen naar programmatie voor de FPGA. Als ontwikkelaar moet je weinig meer doen dan de code die je wil draaien voeden aan de tool, waarna die in essentie een accelerator op maat boetseert uit FPGA-klei.

“Het mooiste voorbeeld hiervan vind je bij het Cern”, weet Scraba. “De experimenten die de onderzoekers daar uitvoeren genereren honderden terabytes per seconde aan data. Die moet op enorme schaal geanalyseerd worden via inferentie. De mensen van het Cern zijn fysisci, geen IT-specialisten. Met de beschikbare tools konden ze Alveo-FPGA’s in serverracks in het laboratorium echter zelf programmeren tot accelerators.”

Toekomst

Uiteindelijk komt het erop neer dat algoritmes het snelst en het efficiëntst draaien op hardware die de structuur van de software weerspiegelt. In bepaalde gevallen is dat een parallelle structuur die overeenkomt met een gpu, maar heel vaak is dat niet zo. Een chip op maat biedt dan een betere oplossing, maar dat is niet haalbaar in de praktijk. De FPGA maakt het mogelijk om die chip op maat virtueel te creëren via bouwstenen op een speciaal daarvoor ontwikkeld stuk hardware.

Algoritmes draaien het snelst en het efficiëntst op hardware die de structuur van de software weerspiegelt.

Combineer die realiteit met de mogelijkheid om FPGA-geaccelereerde servers via een cloudmodel aan te bieden, software die ervoor zorgt dat je geen hardware-expert hoeft de zijn om de FPGA te programmeren en je begrijpt het potentieel van de chips. De opkomst van steeds meer inferentieworkloads die snelheid en efficiëntie vereisen, latency die laag moet blijven en de mogelijkheid voor iedereen om met FPGA-acceleratie aan de slag te gaan, zorgen ervoor dat het veld in de toekomst alleen nog maar zal groeien.