Door meerdere chiplets te combineren in één chip hoopt Intel Moore’s Law in leven te houden. Het zet tegelijk UCIe in de kijker als universele chiplet interconnect gebaseerd op PCI Express om de toekomst vorm te geven.

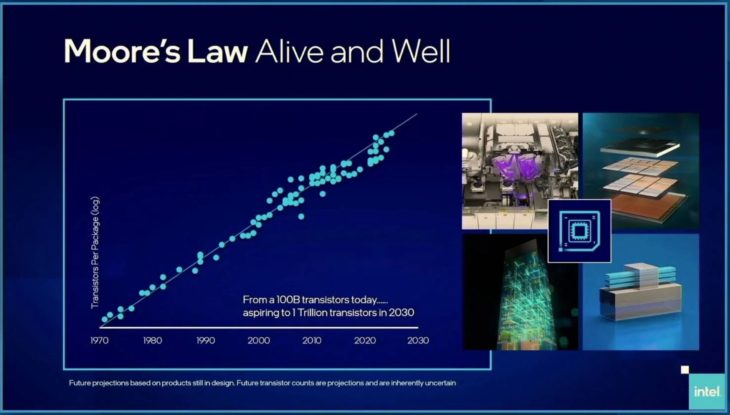

Intel en Moore’s Law, beiden zijn al lang met elkaar getrouwd en kunnen elkaar moeilijk loslaten. Na een aantal verloren jaren door een lastige overstap naar EUV-lithografie lijkt de chipfabrikant opnieuw op koers om grote stappen te zetten. Op de Hot Chips-conferentie verkondigt Intel CEO Pat Gelsinger dat Moore’s Law nog steeds relevant blijft en al zeker tot 2030 realistisch is.

“Vandaag bevat een chip tot honderd miljard transistoren in één pakket. Tegen 2030 kunnen we dat opkrikken tot één biljoen transistoren, een tienvoud van wat vandaag kan.”

Om dat mogelijk te maken, is een chip niet langer één monolithisch geheel. Sinds de 12de generatie Alder Lake-processors bestaat een chip uit krachtige prestatiekernen en zuinige efficiëntiekernen. Gelsinger tekent een toekomst uit waar verschillende chiplets op één chip worden gehuisvest.

Dat in combinatie met Ribbon FET, een nieuwe transistor-architectuur dat toekomstbestendig richting ångström kan evolueren, moet Intel genoeg munitie geven om zich te wapenen voor nieuwe innovaties tot zeker 2030.

Intel Meteor Lake en Sapphire Rapids

Met vele chiplets in één verpakking evolueert de traditionele processor op termijn naar een SOP (System On Package). Er is niet enkel ruimte voor CPU-prestaties, ook AI-acceleratoren, geheugen of voedingsfuncties kunnen mee op de chip. Nieuwe 3D-verpakkingstechnieken maken het mogelijk om meerdere chiplets op elkaar te integreren.

Intel Meteor Lake zou de eerste zijn die de chiplet-technologie optimaal benut en moet vanaf volgend jaar beschikbaar zijn. Arrow Lake wordt de tweede generatie die daarop volgt.

Binnen het datacentersegment mag Sapphire Rapids de spits afbijten volgend jaar met de nieuwste generatie Intel Xeon Scalable CPU’s.

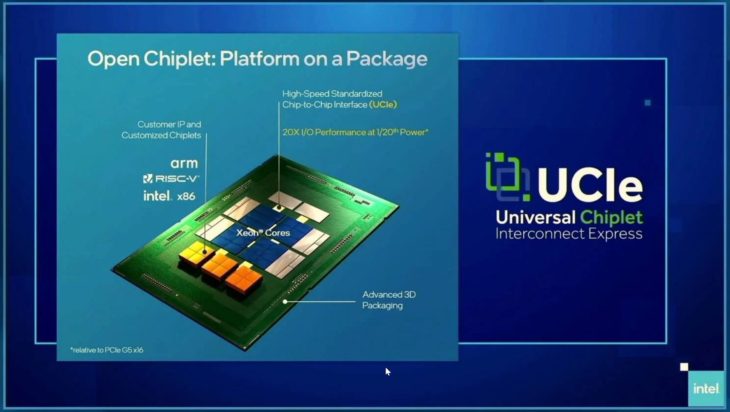

UCIe-technologie als standaard

Samen met alle ambities wijst Gelsinger ook naar Intels eigen UCIe-technologie, kort voor Universal Chiplet Interconnect Express. Hij pusht UCIe sterk om de standaard te worden. Het helpt dat de technologie gebaseerd is op PCI Express om de slaagkans te verhogen.

“Dankzij UCIe kan je bijvoorbeeld twee chiplets van Intel nemen, één uit de fabriek van TSMC, misschien nog stroomcomponenten van Texas Instruments en een I/O-component van Global Foundries.” Het spreekt voor zich dat Intel de beste technologie in huis heeft om die chiplets te verpakken op één chip met 2D- of 3D-technologie, maar je kan de chip ook bij een andere leverancier laten assembleren.

Al die technologie moet het mogelijk maken om Moore’s Law en de bijhorende tweejaarlijkse verdubbeling van het aantal transistoren te handhaven.