AMD geniet van het verlies aan momentum van Intel om zich opnieuw op niveau te hijsen. Met de Epyc-serverchips doorbreekt het de Xeon-hegemonie van Intel en Epyc Rome belooft een flinke stap voorwaarts om twijfelaars helemaal gerust te stellen.

AMD heeft nieuwe details onthuld rond Epyc Rome (Zen 2-architectuur), de nieuwe serverchips die voor het eerst op 7 nm worden gebakken. Met de eerste Epyc (Zen 1-architectuur) chips zette AMD vanuit het niets zichzelf sterk op de kaart, maar er is bevestiging nodig en een roadmap om bedrijven te overtuigen om in AMD te investeren. Epyc Rome bevestigt en overtreft de verwachtingen met een beloftevolle eerste onthulling en een blik op de Epyc-roadmap.

Volgens AMD CTO Mark Papermaster zal de tweede generatie Epyc-chips een flinke verbetering bevatten vergeleken met het originele ontwerp. Floating point throughput wordt verdubbeld dankzij 256-bit AVX2 registers. Load/Store bandbreedte wordt ook verdubbeld volgens Extremetech. De dispatch en retire bandbreedte verhoogt, net als de micro-op cache.

Verdubbeling

Al deze verbeteringen zorgen ervoor dat de Epyc-prestaties flink de hoogte in schieten. Het enige wat niet zeker is, is de verlaging van de kloksnelheid wanneer het AVX2 draait. Intel moet dit namelijk wel doen met hun Xeon-chips.

Lees dit: Intel moet AMD agressief beconcurreren in de servermarkt

AMD biedt PCIe 4.0-ondersteuning aan Epyc Rome maar biedt tegelijk ook ondersteuning voor de eerste generatie Epyc chipsets en de volgende ‘Milan’-generatie Epyc 3-chips. Dit betekent dat de cpu’s zowel PCIe 3.0 als 4.0 kunnen gebruiken, afhankelijk van het platform in kwestie.

Er wordt nog niet gegoocheld met aantal kernen, maar AMD spreekt consequent van een verdubbeling aan rekenkracht. Vermoedelijk zullen de nieuwe Epyc 2-chips tot 64 kernen hebben, vergeleken met 32 kernen van de huidige reeks.

Nieuw ontwerp

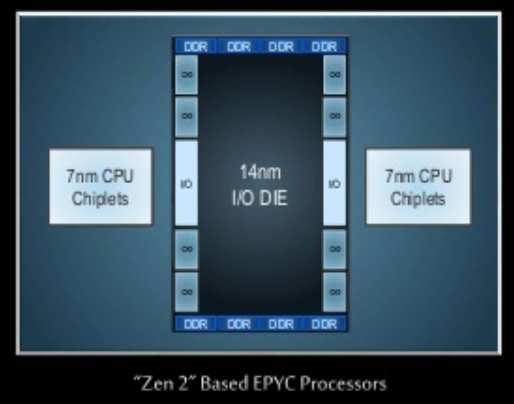

De grootste vernieuwing zit hem in de implementatie van de Infinity Fabric en memory controllers waarmee de verschillende dies op een chip met elkaar communiceren. In de eerste generatie Epyc had elke die zijn eigen memory controllers, Infinity Fabric-links en PCIe-kanalen. Nu centraliseert AMD al deze IO in een 14 nm I/O die en zitten daarrond de 7 nm dies met de pure processorkracht. In de centrale I/O die zitten acht memory controllers, acht Infinity Fabric-poorten evenveel PCIe-kanalen.

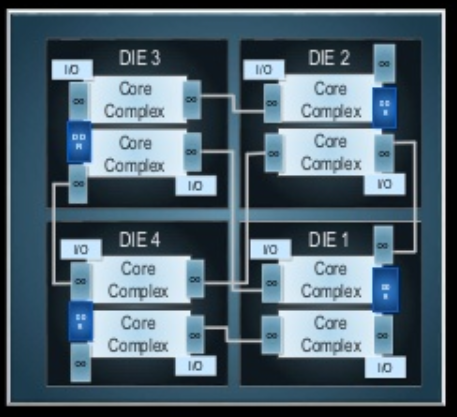

AMD Zen 1-architectuur met per die een Core Complex met eigen memory controllers, Infinity Fabric- en PCIe-kanalen.

AMD Zen 2 centraliseert alle I/O in een 14 nm die en bevat acht memory controllers, acht Infinity Fabric-poorten evenveel PCIe-kanalen.

Op deze manier elimineert AMD een belangrijke flessenhals present in de eerste generatie Epyc-chips. Daar kon er memory latency optreden wanneer een kern van die twee geheugen nodig had van een kern uit die vier. Nu verloopt alles centraal en wordt die memory latency geëlimineerd. Het zorgt tegelijk ook voor een rechtlijniger ontwerp per cpu-die.

Wie enthousiast wordt, gaat helaas nog even geduld moeten oefenen. AMD lanceert Epyc Rome ergens in 2019 zonder een exactere timing te geven. Het Zen 2-platform waarop Epyc Rome draait, wordt op dit ogenblik gesampled. Zen 3, de opvolger, bouwt verder op de stap naar 7 nm met verfijningen en optimalisaties en staat gepland voor 2020. Zen 4 zit in de ontwerpfase en krijgt nog geen deadline opgelegd.