Gij zult niet sterven, commandeert de chipindustrie, dus blijft de wet van Moore leven. Eenvoudig is dat niet. De CEO van Imec doet uit de doeken welke nieuwe technologie nodig is om chips te blijven schalen, zodat er genoeg rekenkracht is om de digitalisering van onze maatschappij ook in de toekomst te ondersteunen.

Jezus zou jaloers zijn op de wet Van Moore: niets of niemand is al meer gestorven en herrezen dan de voorspelling van Gorden Moore, medeoprichter van Intel, die al in 1965 vaststelde dat het aantal transistors op een microschakeling grofweg iedere twee jaar zou verdubbelen.

Verplichte verdubbeling

De wet van Moore klinkt bijna als een natuurkundige wet, maar mag je eigenlijk als een juridische regel interpreteren. De transistordichtheid zal niet verdubbelen, ze moét verdubbelen. De voorspelling van Moore overleeft bij de gratie van een internationale verzameling van ingenieurs met een Mensa-IQ en miljarden dollars aan R&D. De straf voor wie zich er niet aan houdt? Een deuk in de reputatie maar vooral een slechtere concurrentiepositie tegenover chipfabrikanten die het moordende innovatietempo wel konden volgen. Vraag dat maar aan GlobalFoundries. Wie? Juist.

Luc Van den hove, CEO van Imec is één van de voorvechters van Moore. “De wet kan en zal niet stoppen”, zei hij in mei op het podium van de Imec Future Summits 2022. “Zowat alle toepassingen in alle velden gaan enorme data-capaciteiten vereisen”, voorspelt hij. Van den hove verwijst onder andere naar de medische sector, maar ziet net als iedereen de trend van digitalisering over sectorgrenzen heen. “Om deze veranderingen aan te drijven, hebben we hoog performante semiconductor-technologie nodig.”

Moore vs. fysica

Dat is gemakkelijker gezegd dan gedaan. Wanneer de wet van Moore in conflict komt met de wetten van de natuurkunde, durft de voortgang al eens te stagneren. Individuele structuren van microchips en zeker transistors naderen het formaat van atomen, waar kwantum-effecten de werking van microchips beginnen te verstoren. Verder is zelfs de fijnste apparatuur ter wereld bijna te grof om deze atomaire structuren op de silicium-wafers aan te brengen. Iets moet plooien, en het zal niet de kwantumfysica zijn.

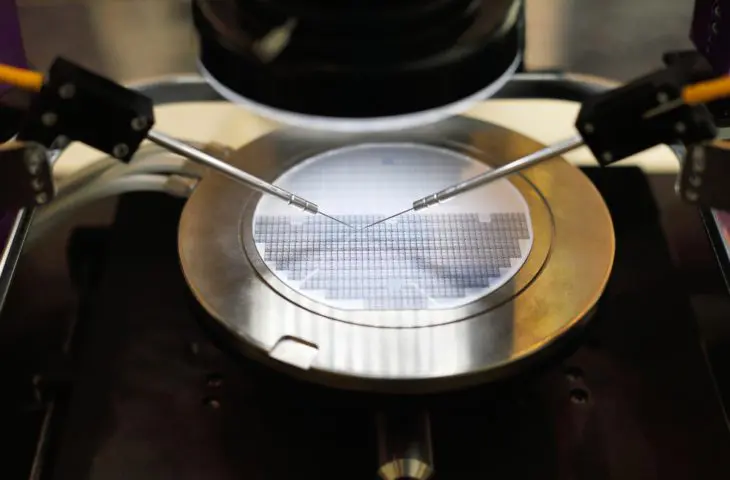

“Traditioneel schalen botst vandaag tegen een muur”, stelt Van den hove zelf vast. “En pure lithografie zeker.” Lithografie is het proces waarbij een machine licht door een soort van stencil op een wafer schijnt. Waar het licht raakt, reageert het met chemicaliën op de wafer en zo worden laag na laag, sjabloon na sjabloon, microchips gebouwd. Het probleem: traditionele lithografie maakt gebruik van licht, en de golflengte van licht is groter dan de vereiste nauwkeurigheid van de stencils. Probeer maar eens een Rubens na te schilderen met een verfroller.

Van den hove ziet een batterij aan oplossingen. Imec is als internationaal gerenommeerde R&D-instelling uitstekend geplaatst om dergelijke problemen als uitdagingen te zien. Het werkt samen met onder andere ASML, dat ’s werelds meest geavanceerde lithografiemachines bouwt, op zoek naar antwoorden.

Van verfroller naar verfpenceel

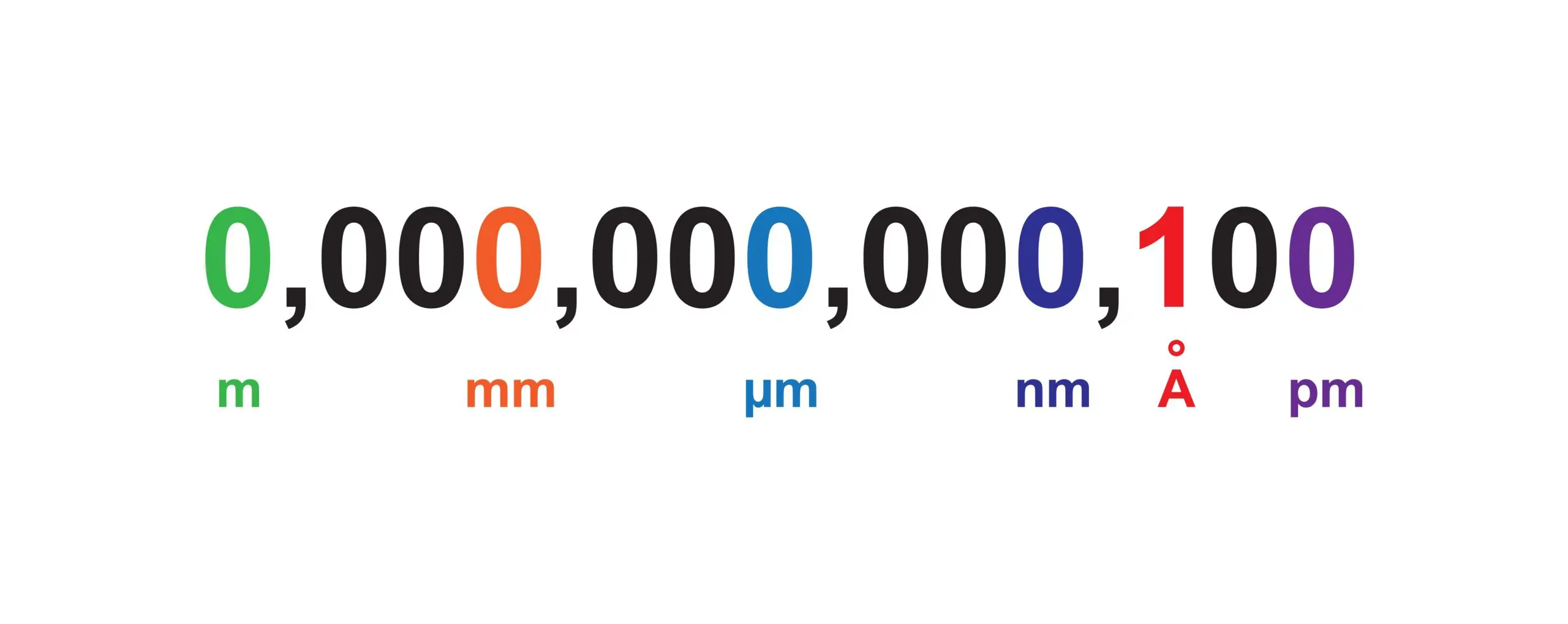

Eén piste hebben we al vaker besproken: fijnere verfkwasten. Is de golflenge van zichtbaar licht te groot? Dan gaan we voor onzichtbaar licht. Lithografie met Extreme UV (EUV) is complex, maar verschijnt vandaag aan meer en meer functionele productiebanden. “EUV zal ons van 5 nm naar 2 nm brengen” voorspelt Van den hove. Maar dat is niet genoeg. “Om kleiner te gaan hebben we een nieuwe versie van EUV nodig met andere lenzen. Die zullen een diameter van 1 meter hebben met een nauwkeurigheid van 20 picometer.

lees ook

Wat je moet weten over processors en nanometers

Daar kan een gewone sterveling zich moeilijk een voorstelling van maken, dus verduidelijkt Van den hove: “Als we dat extrapoleren naar het niveau van de aarde, moeten we de aardbol polijsten met een afwijking van een dikte van maximaal een menselijk haar.” Hij lijkt zich echter geen zorgen te maken. Samen met ASML verwacht Imec zogenaamde High-NA EUV tijdig klaar te hebben.

Nieuwe muren om te slopen

Op naar nieuwe problemen. “Zowat alle winsten op vlak van prestaties, dichtheid en kosten komt er dankzij de verkleining van één component: de transistor.” Volgens Van den hove zijn transistors vandaag zo klein dat chipdesign tegen een nieuwe muur botst. Of liever: nieuwe muren. “De geheugenbandbreedte kan niet mee met de CPU-prestaties”, weet hij. De processor kan niet sneller werken dan data en instructies beschikbaar zijn uit het geheugen. Dat is de geheugenmuur. “Verder wordt het moeilijker om voldoende stroom in de chip te krijgen, maar ook om de warmte eruit te halen. De koeling kan niet volgen.” Zo lopen we tegen de stroommuur aan.

Het wordt moeilijker om voldoende stroom in de chip te krijgen, maar ook om de warmte eruit te halen.

Luc Van den hove, CEO Imec

Van den hove wil deze muren slopen. Dat moet, wil Moore in leven blijven. Voor de stroommuur is al een oplossing in zicht. “De stroomdistributie loopt nu van de top van de wafer door meer dan tien lagen naar de transistor. Dat moet naar de achterkant. We gaan powerrails in de wafer zinken.” Nano-through-Silicon-via’s heet dat dan. De technologie is complex, maar het principe is simpel: bouw eerst een geraamte voor de stroomvoorziening, met de transistors daarop. Dat geeft meer flexibiliteit aan de interconnects die bovenop de transistors zitten en ze tot logische schakelingen binden, en maakt het geheel efficiënter.

Om de geheugenmuur neer te halen, moet geheugen dichter naar de chip komen. Van den hove kijkt naar 3D-structuren op interposers met rechtstreekse siliciumverbindingen naar DRAM-blokken. Chips moeten in één 3D-pakketje met geheugen zitten. Daar bovenop ziet hij een rol weggelegd voor optische interconnects.

Nieuwe transistors

We zijn nog niet aan de nieuwe patatten, zeggen ze dan op onze Kempische redactie. Maar de roadmap ligt al wel paraat. Imec heeft een traject klaar dat ons van 2018 en 7 nm naar 2036 en 0,2 nm of 2 ångström brengt. EUV en H-NA EUV spelen daarbij een grote rol, net als complexere 3D-designs maar natuurlijk ook nieuwe ontwerpen voor de transistors zelf.

Vandaag bouwen vrijwel alle chipfabrikanten microchips met FinFET-transistors, maar dat design krijgt teveel last van kwantumstoringen. Samsung startte net chipproductie met de opvolger: de Gate-All-Around (GAA) of nanosheet-transistor. Die wordt volgens Van den hove essentieel vanaf 2 nm. TSMC en Intel zijn akkoord, en blijven voor 3 nm-chips nog even met FinFET werken.

Hoewel de GAA-transistor al hypermodern is, kijken Imec en Van den hove verder naar de toekomst. Een opvolger wordt al klaargestoomd: de CFET-transistor. Die zal optimaal van drie dimensies gebruikmaken en is een complexe verticale opvolger van GAA. Op termijn verwacht Van den hove dat chipproducten nieuwe ultradune 2D-monolayer-materialen zullen incorporeren met een atomische dikte. Bij Imec weten ze met andere woorden nog wel even wat te doen.

Moore blijft leven, Von Neumann moet dood

Op de lange termijn moet volgens Van den hove de Von Neumann-architectuur op de schop. Die evolutie zien we nu al. Von Neumann zag de digitale computer als een systeem met input, een centrale verwerkingseenheid en output. “We moeten evolueren naar domein-specifieke architecturen”, verwacht Van den hove, “zoals het brein werkt.”

Dat impliceert dat de CPU een steeds kleinere rol zal krijgen ten voordele van op maat gemaakte schakelingen voor specifieke workloads. “Als we deze visie volgen, zal de wet van Moore niet stoppen”, verwacht de Imec-CEO. Von Neumann wordt opgeofferd om Moore onder de levenden te houden.

In 14 jaar van nanometer naar ångström

Wat betekent dat nu concreet? Voor 3 nm zitten we op schema: daarvan verwacht Imec dit jaar volumeproductie en Samsung heeft de toon al gezet. TSMC zal snel volgen. Tegen 2024 moeten de eerste 2 nm-chips van de band rollen met GAA Nanosheet-transistors. Vanaf 2026 mogen we dan in ångström (Å) meten met 1,4 nm of 14 Å.

lees ook

Welke uitdagingen moet de chipsector overwinnen voor het een oplossing voor Alzheimer heeft?

Tegen 2030 zakken we echt onder de 1 nm met 7 Å en is GAA tegen zijn limieten aan. De deur naar sciencefiction opent in 2032 met 5 Å en CFET, met een traject naar 3 Å en 2036 met materialen en interconnects op atomaire schaal. Is dat optimistisch? Misschien wel. De sprong van 14 nm naar 10 nm heeft in ieder geval langer geduurd dan verwacht, onder andere omwille van de moeilijke implementatie van EUV. Intussen lijkt de verkleiningstrein wel opnieuw op kruissnelheid.

Duidelijke landkaart

Het belangrijkste feit is dat chipbouwers niet in het duister tasten. Er ligt een duidelijk pad naar verkleining klaar. De transistor kan nog een stuk krimpen, designs kunnen stroomefficiënter en geheugen kan dichter naar de chip komen. Het is moeilijk, maar als we Van den hove mogen geloven, hoeft dat geen probleem te zijn. Moeilijk gaat ook, en Moore moet overeind blijven. De succesvolle digitalisering van de maatschappij hangt ervan af.