Cadence Design Systems, dat software bouwt voor chipontwikkelaars, integreert AI in zijn platform. Die moet een deel van het designwerk uit handen van de ingenieurs halen.

Cadence introduceert Cerebrus Intelligent Chip Explorer. Dat is een AI-platform bedoeld voor architecten van microchips. Cadence bouwt chipdesign-software. Dat zijn tools waarmee de ingenieurs van onder andere Nvidia en AMD aan de slag gaan wanneer ze nieuwe CPU’s en GPU’s ontwikkelen. De nieuwe AI-suite zal hen nu helpen met die taak.

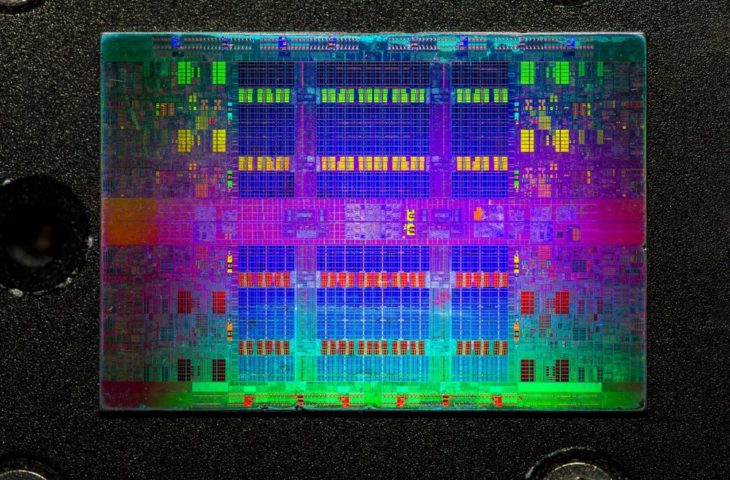

Chipdesign is een erg complexe taak. Ingenieurs en architecten proberen steeds snellere en efficiëntere microchips te ontwerpen, maar dat kan niet manueel. Een moderne chip bevat echter miljarden transistors gecombineerd in logische schakelingen. Die worden niet manueel uitgetekend. In de plaats daarvan vertrouwen ontwikkelaars op software zoals die van Cadance om meer high level-concepten te vertalen naar de detailweergave op transistorniveau.

AI en optimalisatie

Daarbij komt heel veel optimalisatie kijken. In de regel werken ingenieurs met een initiële blauwdruk waarin ze uitwerken hoe data doorheen een chip zal bewegen. Vervolgens verbeteren ze dat concept met kleine aanpassingen, waarbij ze zoeken naar efficiëntiewinsten. Het iteratieproces neemt meer tijd in beslag dan het bedenken van de eerste blauwdruk.

De Cerebrus-suite van Cadence gaat ingenieurs nu helpen met die taak. Daartoe zet de AI-suite reinforcement learning in. Dat is een techniek waarbij een algoritme zonder training door voorbeelden zelf opzoek gaat naar het antwoord op een probleem.

In dit geval gaat het om een optimalisatievraagstuk. De ingenieurs geven een blauwdruk en een vooropgesteld efficiëntiedoelwit aan de Cerebrus-suite. Die maakt vervolgens allerhande kleine aanpassingen op zoek naar een beter resultaat. Verbetert een aanpassing de efficiëntie, dan krijgt het algoritme een soort beloning waardoor het aangemoedigd wordt in die richting verder te denken. Het omgekeerde gebeurt bij een iteratie die niet relevant is. Zo ontdekt de software volledig zelf het pad naar een betere chip, zonder extra menselijke hulp.

Vloerplan

Wanneer het design geoptimaliseerd is, moeten ingenieurs dat vertalen naar hardware. Daarbij is het niet eenvoudig om alle componenten en schakelingen optimaal op een chip te plaatsen. De bouw van zo’n vloerplan is opnieuw een optimalisatievraagstuk en ook daar helpt de AI van Cadence bij. De software treedt zo in de voetsporen van Google, dat vorige maand in een paper in Nature uit de doeken deed hoe AI de uitwerking van finale instructies voor de bouw van een microchip drastisch kan versnellen.

Chipdesign met de hulp van AI belooft de toekomst te worden. Het is verrassend hoe snel het concept tot bij de designers geraakt. Wat vorige maand nog een onderzoeksprimeur was voor Google, zit vandaag in de Cerebrus-software van Cadence.