Om tegemoet te komen aan de steeds hogere prestatie-eisen in datacenters zijn krachtigere gpu’s nodig. Een studie toont nu aan dat het tijd is om waferscale-chips van onder het stof te halen.

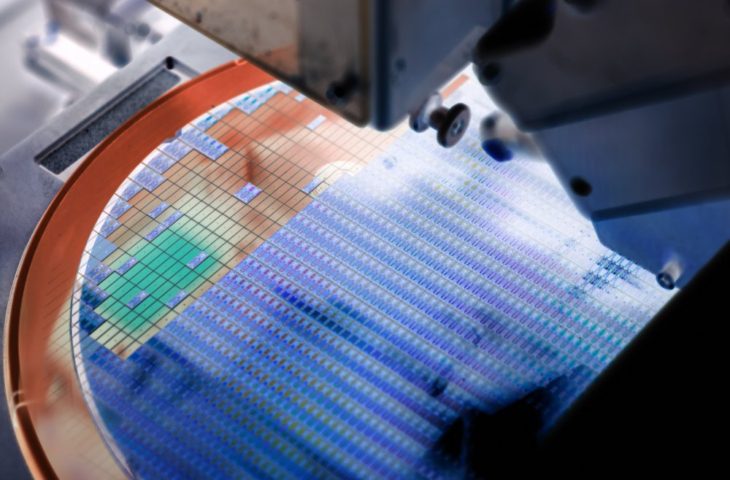

Researchers van de universiteiten van Californië en Illinois tonen in een studie aan dat de tijd rijp is om waferscale-gpu’s een nieuwe kans te geven. Waferscale-chips zijn een idee uit de jaren ’80, dat destijds werd afgevoerd wegens praktisch onhaalbaar. De chips zijn erg groot, zodat er slechts enkele op een silicium-wafer passen. Op de chip kunnen dan rekenkracht, interconnects en geheugen meteen worden gecombineerd. Die aanpak zorgt voor veel snellere hardware met een lagere latency.

Geen PCB meer

Een waferscale-chip is met andere woorden een chip die komaf maakt met het printed circuit board (PCB). Normaal worden chips en masse op wafers gebakken, die vervolgens in stukjes worden geknipt. De individuele chips worden dan met andere relevante chips verbonden via het PCB. Door de hele chip meteen op het siliciumsubstraat te ontwikkelen, schieten snelheid en efficiëntie de hoogte in.

In de jaren ’80 waren fabricagetechnieken onvoldoende vergevorderd om een dergelijke aanpak te laten slagen. Vandaag staan we een stuk verder en de onderzoekers tonen in hun studie aan dat er principieel geen bezwaren zijn tegen waferscale-fabricage.

Schaalbare interconnect

De onderzoekers ontwikkelden het Silicon Interconnect Fabric (SI-IF) om chipets op een wafer met elkaar te verbinden. SI-IF neemt de rol van het PCB over en is veel sneller. Intel en TSMC dachten ook al in die richting met hun eigen EMIB (Embedded Multi-die Interconnect Bridge)- en CoWoS (Chip on Wafer on Substrate)-technologieën, maar die zijn slechts in staat om een handvol chiplets met elkaar te linken. SI-IF zou veel schaalbaarder zijn.

Door alle onderdelen op de silicium wafer te ontwikkelen, wordt een PCB overbodig.

Dat illustreerden de researchers met een prototype waarbij ze tien 4 mm²-chips met elkaar verbonden op een waferscale-chip. Ze berekenden dat hun interconnect in staat moet zijn om zeker 40 chiplets met elkaar te verbinden. Dat betekent concreet dat het mogelijk is om één grote chip te bouwen waarop 40 gpu-dies samenwerken als één geheel. Het resultaat zou meer dan vijf keer sneller zijn dan wanneer je diezelfde 40 dies op een andere manier probeert te combineren.

Veelbelovende piste

Het onderzoek toont aan dat waferscale een interessante piste is om te volgen in de zoektocht naar steeds meer rekenkracht. De researchers richtten zich op gpu’s, omdat die parallel rekenwerk moeten verrichten en dat schaalt natuurlijk netjes wanneer je meerdere gpu’s tot één geheel combineert.

De oplossing zou interessant zijn voor gebruik in datacenters waar analytics, AI en machine learning steeds belangrijker worden. Het formaat, de prijs en het stroomverbruik van waferscale-hardware betekenen bovendien dat we de technologie niet meteen op pc-schaal hoeven te verwachten. Eén waferscale-die die 40 gpu’s combineert, heeft nog steeds voldoende elektriciteit nodig om die 40 gpu’s te laten zwoegen. Bovendien bestaat de hardware uit een flinke hap van één wafer, en die dingen kosten geld.

Gerelateerd: Hoe Intel zich schrap zet voor de lancering van een eigen gpu-reeks