Intel lanceert met Foveros een 3D die stacking-techniek waarbij verschillende dies op elkaar kunnen worden gestapeld. De chipgigant wil op termijn alle chips volgens dit concept maken en volgt zo het voorbeeld van AMD met Epyc Rome.

In 2019 gaat Intel een nieuwe stapeltechniek gebruiken onder de codenaam Foveros. Het nieuwe concept laat toe om complexe dies op elkaar te stapelen. Zo kan Intel op maat verschillende componenten mixen en die in optimale omstandigheden maken.

Het stapelen van dies gebeurt al veel langer bij ARM-chips onder de noemer System-on-Chip (SoC). Dit concept stapelt bijvoorbeeld een geheugenpakketje bovenop een cpu met een honderdtal interconnecties tussen de twee. Het formaat en de prestaties zijn echter een flessenhals bij deze stapeltechniek.

Microbumps

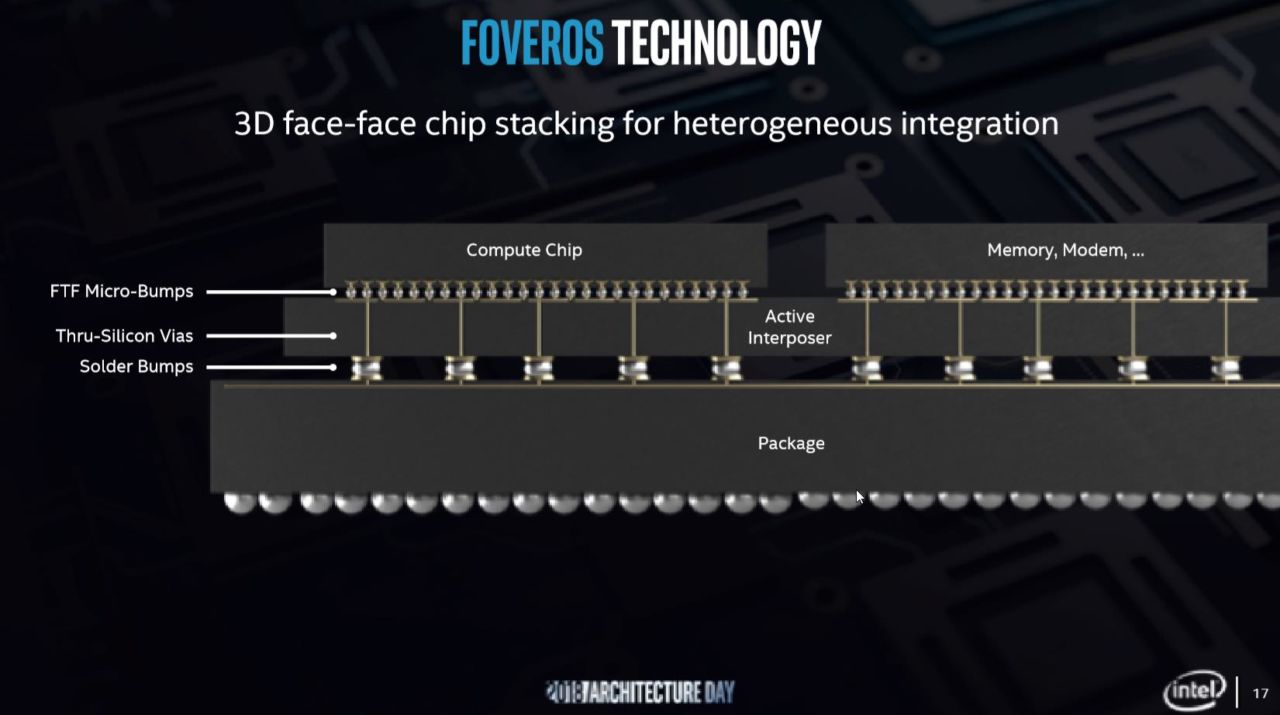

Foveros maakt als interconnect gebruik van etched silicon om veel meer interconnecties mogelijk te maken aan een hogere snelheid. Intel heeft deze techniek al gebruikt in een vergelijkbare vorm bij Kaby Lake-G, Intels allereerste processor dat een Intel CPU, AMD GPU en HBM (High Bandwith Memory) combineert.

Intel bouwt daarop verder met Foveros maar maakt nu gebruik van duizenden ‘microbumps’ met directe face-to-face connecties tussen de gestapelde onderdelen. De interposer is ook niet enkel een circuit met enkele banen maar een volwaardige chip met eigen logic ingebouwd.

Lees dit: Intel moet AMD agressief beconcurreren in de servermarkt

De SoC inclusief geheugen meet 12 bij 12 millimeter volgens Hardware.info. Intel heeft 828 contactpunten per mm² en chips kunnen behalve naast elkaar op de interposer ook bovenop elkaar worden gestapeld. Het stand-by verbruik is 2 mW.

Chiplets

De flexibiliteit van Foveros betekent dat essentiële processor-elementen kunnen worden verdeeld over verschillende dies. Zo kan Intel hoge prestatie cpu-kernen bakken op 10 nm en I/O-connectiviteit (usb 3.1, wifi, ethernet, PCIe, enz.) op 22 nm of 14 nm. IO heeft niet de nieuwste prestatiewinsten nodig omdat ze beperkt zijn door een fysieke interface. Wanneer we verder naar de toekomst kijken, kunnen die verschillende componenten nog meer worden opgesplitst in aparte wifi-blokken, usb, enz.

Het doet heel sterk denken aan het Big.Little-verhaal dat ARM al veel langer brengt. Dit concept combineert één of meerdere hoge prestatiekernen met zwakkere kernen. Volgens Intel zou de Windows 10 October 2018 Update al de nieuwe Foveros-architectuur ondersteunen.

Intel kan al deze elementen stevig verpakken in drie dimensies wat de voetafdruk van de chip grondig verkleint. Het zal in de nabije toekomst verschillende chiplets kunnen mixen en matchen voor verschillende toepassingen.

AMD Epyc 2

Intel plant om Foveros-producten in de tweede helft van 2019 te lanceren. De technologie is alvast klaar voor massaproductie. Intel wil het in mainstream processors gebruiken, niet enkel gespecialiseerde of op maat gemaakte processors. Intel spreekt over chips met één 10 nm hoge prestatiekern en vier 10 nm atom-kernen.

De chipgigant volgt met Foveros dezelfde richting die AMD recent insloeg. Met de Epyc Rome serverchips voor 2019 werkt AMD met een design met twee 7 nm chiplets en een centrale 14 nm I/O die voor alle connectiviteit. Epyc Rome gebruikt 8 Infinity Fabric-kanalen om alle informatie tussen de twee chipkernen te sturen en elke chiplet bevat verschillende dies met een vast aantal kernen.

Gerelateerd: AMD toont Epyc 2 met radicaal ontwerp en sterke prestatiewinsten