De verkleining van chips volgt tot op vandaag nog steeds de wet van Moore met een procesverkleining elke twee jaar. TSMC is klaar om te starten met de risicoproductie van chips met een EUV-laser, maar gaat heel gestaag te werk.

De race naar steeds kleinere productieprocessen eist zijn slachtoffers. Globalfoundries heeft eind augustus laten weten dat het de overstap naar 7 nm stopzet en focust op verdere optimalisaties van 14 nm en 12 nm FinFET. Intel heeft het moeilijk om de stap naar Extreme Ultra Violet (EUV) en een verdere verkleining te zetten en moest zijn hoge standaarden recent wat versoepeld. Samsung is vandaag al bezig met risicoproductie van EUV, maar enkel voor eigen gebruik. TSMC start nu ook met risicoproductie van EUV en heeft een plan voor de komende drie jaar.

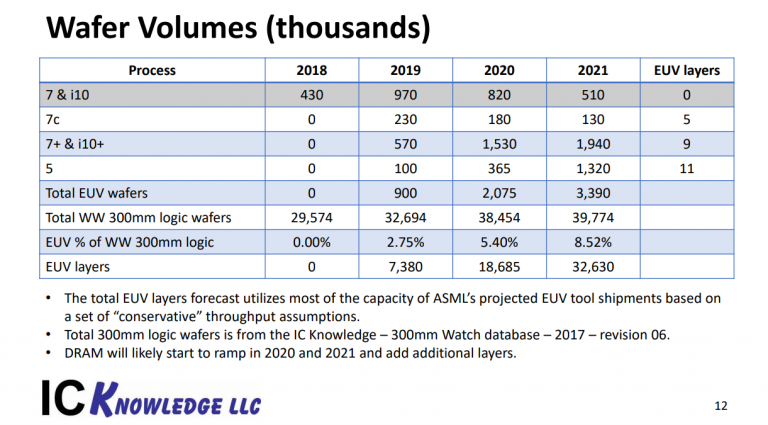

Vandaag worden er al 7 nm-chips gebakken bij TSMC, maar die maken gebruik van een klassieke Argon Fluoride (ArF)-laser. Het wil in 2019 ongeveer 900.000 EUV-wafers maken, goed voor 2,75% van de totale productie. In 2020 en 2021 moet dat 5,40% en 8,52% zijn. Er wordt al meer dan twee decennia gewerkt aan EUV; elke stap voorwaarts is een belangrijke voor de verdere verkleiningen van chips.

EUV-machines

Aan EETAsia discusses laat TSMC weten dat het vanaf Q2 2019 voorzichtig start met 5 nm op EUV met 100.000 wafers. Dat aantal zou verdrievoudigen in 2020 en vertienvoudigen in 2021. De 5 nm-node zou in totaal tot 14 lagen kunnen ondersteunen, maar heeft als grootste probleem dat er nog geen pellicle (beschermend schild/vlies dat de wafer beschermt tegen afval) is.

Het is ontzettend moeilijk om zo’n vlies te maken voor EUV omdat extreem uv-licht haast door alles geabsorbeerd wordt, inclusief de lucht rondom. Daarom moeten EUV-machines in een vacuà¼m opereren.

De EUV-productie van de huidige 7 nm-chips voegt niets extra toe aan de bestaande 7 nm-chips die van de band rollen. Ze dienen enkel om de kosten te drukken en om verdere verkleiningen te kunnen ontwikkelen die met een ArF-laser steeds moeilijker wordt.

5 nm-node

De nieuwe 5 nm-node brengt volgens Extremetech een prestatiewinst van 20% of een gelijkwaardige energiebezuiniging met zich mee. Qua oppervlakte spreekt TSMC over een verkleining van 45%. Het is voorlopig nog onduidelijk bij alle chipproducenten wat de volgende stap is na 5 nm. Vooral het vlies is op dit ogenblik het grootste pijnpunt waar nog geen oplossing voor bestaat. Daarnaast nemen steeds meer bedrijven afstand van de race naar kleinere chips met enkel Intel, TSMC en Samsung als enige aanbieders.

Van zodra TSMC in Q2 2019 start met de risicoproductie van 5 nm zou het tot één tot anderhalf jaar kunnen duren voordat de chips klaar zijn voor massaproductie. Tegen die tijd zou Intel zijn 10 nm-proces onder de knie moeten hebben. AMD bakt zijn chips bij TSMC, wat de nodige ruimte moet geven om de huidige groei verder te zetten met kleinere chips dan de concurrent.